SC-OBC Module A1 Development Board Product Manual

1. はじめに

このたびは SC-OBC Module A1 Development Board をご利用いただき、ありがとうございます。

SC-OBC Module A1 Development Board は、SC-OBC Module A1の初期の開発を円滑に行えることを目的としており、ソフトウェアやFPGAの開発に必要な以下の各種インタフェースが搭載されています。

-

DCジャックを始めとする柔軟性の高い電源インタフェース

-

FPGA JTAG、PIC ICSP、Zephyer ConsoleなどのDEBUGインタフェース

-

CAN、User IOなどの通信インタフェース

また、User IOを用いて構築する回路を容易に実装する事を目的とした Universal Areaを備え、初期のシステム検討や BBM開発を手助けします。

2. 注意事項

2.1. 安全に関する注意事項

本製品を安全にご使用いただくため、特に以下の点にご注意ください。

-

ご使用の前に必ず製品マニュアルおよび関連資料をお読みになり、使用上の注意を守って正しく安全にお使いください。

-

水・湿気・ほこり・油煙等の多い場所、また腐食性ガス、可燃性ガス等の環境下でのご使用はご遠慮ください。火災、故障、感電などの原因になる場合があります。

-

本製品は長時間連続動作させている場合など、発熱により高温になる場合があります。周囲温度や取扱いによってはやけどの原因となる恐れがあるため、長時間連続動作させている間、または電源切断後本体の温度が下がるまでの間は、取扱いにご注意ください。

-

SC-OBC Module A1 Development Board には民生用の一般電子部品が使用されております。機能・精度において極めて高い信頼性・安全性が必要とされる、宇宙、航空、医療、原子力、運輸、交通、各種安全装置などで人命、事故に関わる用途および多大な物的損害を発生させる恐れのある用途でのご使用はご遠慮ください。

-

発煙や発火、異常な発熱があった場合には、すぐに電源を切ってください。

2.2. 取扱い上の注意事項

本製品の取扱い時には以下のような点にご注意ください。

-

コネクタへは無理に力を加えて破損することのないよう注意してください。

-

本製品や周辺回路に電源が入っている状態で、活線挿抜対応インタフェース(USB、SC Bus)以外へ挿抜は行わないでください。

-

本製品を開封するときは静電気にご注意ください。

-

連続的な振動(車載等)や衝撃が発生する環境下でのご使用は、製品寿命を縮め、故障が発生しやすくなりますのでご注意ください。

-

本製品を仕様範囲を越える条件において使用した場合、故障の原因となりますので、ご注意ください。

2.3. 製品の保管について

-

保管環境として推奨する温度・湿度条件は以下のとおりです。

推奨温湿度環境 5~30℃/60%RH 以下 -

製品を在庫として保管する場合は、高温・多湿、埃の多い環境、水濡れの可能性のある場所、直射日光のあたる場所、有毒ガス(特に腐食性ガス)の発生する場所を避けて保管してください。

-

温度変化の少ない場所に保管してください。保管時の急激な温度変化は結露が生じ、金属部の酸化、腐食などが発生し、はんだ濡れ性に影響が出る場合があります。

-

本製品を保管する際は、静電気を帯びやすいビニール袋やプラスチック容器などは避け、帯電防止処理された収納容器を使用してください。

-

金メッキ部分に素手で触れた場合、劣化が早まるためご注意ください。

3. 用語の定義

本書の中で使用する用語の定義は以下の通りです。

| 用語 | 説明 |

|---|---|

OBC |

SC-OBC Module A1 を示す。 |

TRCH |

Timing, Reset, Config & Health Controller の略。OBCでは PIC16LF877 を採用している。 |

FPGA |

Field Programmable Gate Array の略。OBCではAMD(旧 Xilinx)製 Artix-7 を採用している。 |

Dev Board |

SC-OBC Module A1 Development Board を示す。 |

Universal Area |

Dev Board上に2.54mmピッチで配置している、未接続のスルーホール群のエリアを示す。 |

UIO1 |

OBCのFPGAにおける User IO Group 1 を示す。 |

UIO2 |

OBCのFPGAにおける User IO Group 2 を示す。 |

UIO3 |

OBCのFPGAにおける User IO Group 3 を示す。 |

UIO4 |

OBCのFPGAにおける User IO Group 4 を示す。 |

VIN_A |

OBCの冗長化された電源入力の片側(A系統)を示す。 |

VIN_B |

OBCの冗長化された電源入力の片側(B系統)を示す。 |

VDD_3V3_SYS |

OBCから出力される電圧を示す。VIN_AおよびVIN_Bへ入力した+5Vから生成された+3.3Vが統合された電圧で、OBCのTRCHなどで使用されている。詳しくはOBCの電源回路の構成を参照。 |

VDD_3V3_IO |

OBCから出力される電圧を示す。VDD_3V3_SYSが更にOBCの回路を経由した後の電圧で、OBCのFPGAなどに使用されている。詳しくはOBCの電源回路の構成を参照。 |

VDD_3V3_DCDC |

Dev Board上に設けられている降圧DC/DCコンバータ回路(IC13)の出力(+3.3V)を示す。 |

VDD_UIO1 |

UIO1が属するFPGA Bankへの電源を示す。 |

VDD_UIO2 |

UIO2が属するFPGA Bankへの電源を示す。 |

4. 製品概要

4.1. 仕様

| Feature | Description |

|---|---|

Interface |

OBC Interface x1 |

TRCH ICSP Interface x1 |

|

DEBUG Interface x1 (FPGA JTAG, CPU JTAG, FPGA Console, TRCH Console) |

|

FPGA JTAG Interface x1 |

|

UIO Interface x4 (UIO1 16pin、UIO2 16pin、UIO3 8pin、UIO4 6pin) |

|

CAN Interface x1 |

|

SC Bus Interface x2 |

|

Main Power Supply x3 (DC Jack x1, Block Terminal x2) |

|

UIO Power Supply x2 (Block Terminal x2) |

|

Power Output x4 (VDD_UIO1, VDD_UIO2, VDD_3V3_SYS, VDD_3V3_IO) |

|

Switch |

Slide Switch for Main Power Supply x1, User Switch x1 |

LED |

Power LED x8, User LED x1 |

Temperature Sensor |

User Temperature Sensor x1 (TI製 TMP175) |

Power Supply |

DC 5V +/-5% |

Operation Temperature |

10~40℃ |

Protection |

Main Power Supply OVP (Over Voltage Protection) x2 |

VDD_3V3_SYS OCP (Over Current Protection) x1 |

|

SC Bus VBUS OCP (Over Current Protection) x1 |

|

ESD Protection (Each Terminal) |

|

Board Size |

200 x 130 mm |

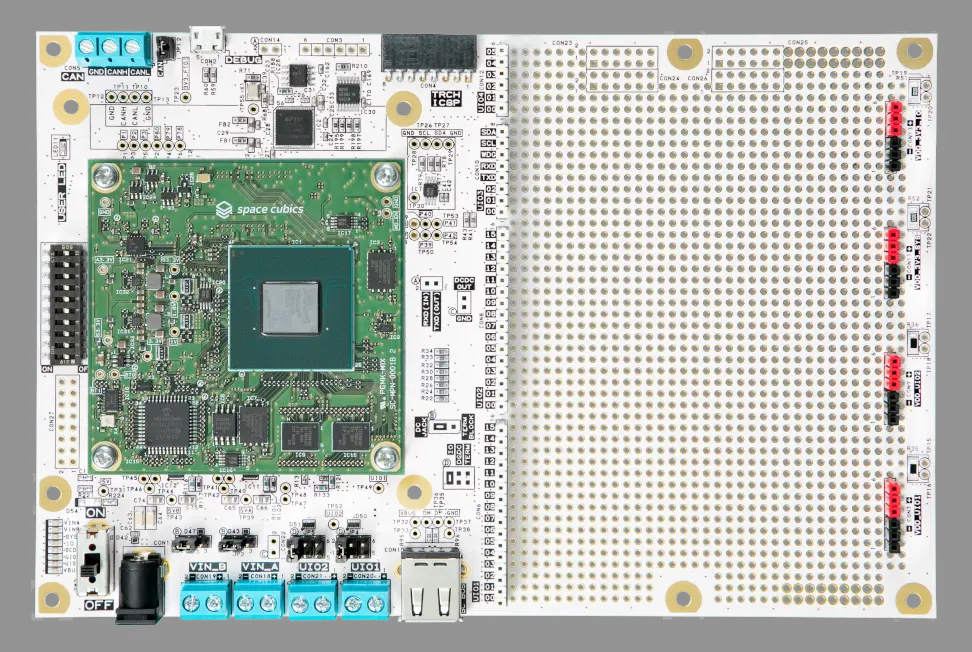

4.2. 外観

Dev Boardの外観を以下に示します。

| 番号 | 名称 | 説明 |

|---|---|---|

1 |

主電源コネクタ |

ACアダプタを接続します。 |

2 |

電源スイッチ |

主電源のON/OFFが可能です。 |

3 |

PowerLED インジケータ |

各種電源の出力状況の判別ができます。 |

4 |

電源セレクタ |

主電源およびUIO電源の入力先の切り替えができます。 |

5 |

OBC |

SC-OBC Module A1を搭載できます。 |

6 |

ユーザースイッチ |

ユーザーが自由に機能を設定できるDIPスイッチです。 |

7 |

ユーザーLED |

ユーザーが自由に使用できる黄緑色LEDです。 |

8 |

CANコネクタ |

CAN通信用のケーブルを接続できる端子台です。 |

9 |

USBコネクタ |

USB Micro-Bプラグを接続できます。FPGA JTAG, CPU JTAG, FPGA UART(Console), TRCH UARTで使用できます。 |

10 |

ユーザー温度センサ |

ユーザーが自由に使用できる温度センサです。 |

11 |

PICkitコネクタ |

Microchip製のPICkitを接続できます。 |

12 |

Universal Area |

ユーザーが自由に使用できる領域です。 |

13 |

USBコネクタ |

表面にUSB Type-Aプラグ、裏面にMicro-Bプラグを接続できます。SC Bus通信の用途で使用できます。 |

14 |

UIO電源コネクタ |

ユーザーがUIO電源を任意の電圧で供給できる端子台です。 |

15 |

主電源コネクタ |

ユーザーがACアダプタ以外で主電源を供給できる端子台です。 |

5. 電源を入れる前に

5.1. 準備するもの

Dev Boardを使用する前に、次のものを必要に応じて準備してください。

作業用 PC |

Linux または Windows が動作し、 1つ以上の USB ポートを持つ PC です。 |

USBケーブル |

FPGAの書き込みやConsoleなどで使用します。Type-A - Micro-Bタイプが必要です。 |

MPLAB PICkit |

Microchip製のデバッカです。TRCHのソフトウェア書き込みに使用します。 |

6. 電気的仕様

6.1. 絶対最大定格

| 項目 | 記号 | 条件 | 最小 | 最大 | 単位 |

|---|---|---|---|---|---|

電源電圧 |

5V, VIN_A_TRM, VIN_B_TRM |

-0.3 |

12 |

V |

|

FPGA I/O バンク電源電圧 |

VDD_UIO1_TRM, VDD_UIO2_TRM |

OBC搭載時 |

-0.3 |

3.6 |

V |

動作温度 |

Topr |

結露なきこと |

-20 |

70 |

℃ |

絶対最大定格は、あらゆる使用条件や試験状況において瞬時でも超えてはならない値です。

絶対最大定格を超える条件下では、デバイスが恒久的に破損する可能性があります。

上記の値に対して余裕をもってご使用ください。

7. インタフェース仕様

Dev Boardにおける各インタフェースの場所と仕様を以下に示します。

| 部品番号 | インタフェース名称 | 形状 | 備考 |

|---|---|---|---|

CON1 |

OBC接続インタフェース |

基板間コネクタ80ピン (0.5mmピッチ) |

挿抜寿命:50回 |

CON2 |

DEBUG インタフェース |

USB Micro-Bコネクタ |

|

CON3 |

FPGA JTAG インタフェース |

ピンヘッダ6ピン (2.54mmピッチ) |

コネクタ未実装 |

CON4 |

TRCH ICSP インタフェース |

ライトアングル ピンソケット8ピン (2.54mmピッチ) |

|

CON5 |

CAN インタフェース |

端子台3ピン (5.0mmピッチ) |

|

CON6 |

UIO1 インタフェース |

ピンソケット16ピン (2.54mmピッチ) |

コネクタ未実装 |

CON7 |

UIO1 Power & GND インタフェース |

ピンソケット VDD3ピン、GND3ピン (2.54mmピッチ) |

コネクタ未実装 |

CON8 |

UIO2 インタフェース |

ピンソケット16ピン (2.54mmピッチ) |

コネクタ未実装 |

CON9 |

UIO2 Power & GND インタフェース |

ピンソケット VDD3ピン、GND3ピン (2.54mmピッチ) |

コネクタ未実装 |

CON10 |

UIO3 インタフェース |

ピンソケット8ピン (2.54mmピッチ) |

コネクタ未実装 |

CON11 |

UIO3 Power & GND インタフェース |

ピンソケット VDD3ピン、GND3ピン (2.54mmピッチ) |

コネクタ未実装 |

CON12 |

UIO4 インタフェース |

ピンソケット6ピン (2.54mmピッチ) |

コネクタ未実装 |

CON13 |

UIO4 Power & GND インタフェース |

ピンソケット VDD3ピン、GND3ピン (2.54mmピッチ) |

コネクタ未実装 |

CON15 |

SC Busホスト インタフェース |

USB Type-Aコネクタ |

|

CON16 |

SC Busデバイス インタフェース |

USB Micro-Bコネクタ |

|

CON17 |

電源入力 インタフェース |

DCジャック |

対応プラグ : 2.1mmΦ (センタープラス) |

CON18 |

電源入力 インタフェース (VIN_A) |

端子台2ピン (5.0mmピッチ) |

|

CON19 |

電源入力 インタフェース (VIN_B) |

端子台2ピン (5.0mmピッチ) |

|

CON20 |

電源入力 インタフェース (VDD_UIO1) |

端子台2ピン (5.0mmピッチ) |

|

CON21 |

電源入力 インタフェース (VDD_UIO2) |

端子台2ピン (5.0mmピッチ) |

|

CON22 |

降圧DC/DCコンバータ出力 インタフェース |

ピンヘッダ2ピン (2.54mmピッチ) |

コネクタ未実装 |

JP1 |

CAN終端抵抗切替 インタフェース |

ピンヘッダ2ピン (2.54mmピッチ) |

|

JP2 |

電源入力切替 インタフェース (VIN_A) |

ピンヘッダ3ピン (2.54mmピッチ) |

|

JP3 |

電源入力切替 インタフェース (VIN_B) |

ピンヘッダ3ピン (2.54mmピッチ) |

|

JP4 |

電源入力切替 インタフェース (VDD_UIO1) |

ピンヘッダ6ピン (2.54mmピッチ) |

|

JP5 |

電源入力切替 インタフェース (VDD_UIO2) |

ピンヘッダ6ピン (2.54mmピッチ) |

|

SW1 |

ユーザースイッチ |

DIPスイッチ |

|

SW2 |

主電源入力 ON/OFF |

スライドスイッチ |

|

LED1~8 |

電源 LED |

LED (黄緑色) |

|

LED11 |

ユーザー LED |

LED (黄緑色) |

7.1. OBC接続インタフェース(CON1)

CON1はOBCとの接続インタフェースです。

搭載コネクタ:AXK5S80047YG(Panasonic)

| ピン番号 | ピン名 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

VIN_A_P1 |

Power |

- |

OBCの主電源(A系統) |

2 |

VIN_A_P2 |

Power |

- |

OBCの主電源(A系統) |

3 |

VIN_A_P3 |

Power |

- |

OBCの主電源(A系統) |

4 |

ULPI_DP |

In/Out |

- |

SC Bus D+信号 |

5 |

ULPI_DM |

In/Out |

- |

SC Bus D-信号 |

6 |

GND |

Power |

- |

電源 (GND) |

7 |

UIO1_00 |

In/Out |

VDD_UIO1 |

UIO1 Bit 0信号 |

8 |

UIO1_01 |

In/Out |

VDD_UIO1 |

UIO1 Bit 1信号 |

9 |

UIO1_02 |

In/Out |

VDD_UIO1 |

UIO1 Bit 2信号 |

10 |

UIO1_03 |

In/Out |

VDD_UIO1 |

UIO1 Bit 3信号 |

11 |

UIO1_04 |

In/Out |

VDD_UIO1 |

UIO1 Bit 4信号 |

12 |

UIO1_05 |

In/Out |

VDD_UIO1 |

UIO1 Bit 5信号 |

13 |

UIO1_06 |

In/Out |

VDD_UIO1 |

UIO1 Bit 6信号 |

14 |

UIO1_07 |

In/Out |

VDD_UIO1 |

UIO1 Bit 7信号 |

15 |

GND |

Power |

- |

電源 (GND) |

16 |

UIO1_08 |

In/Out |

VDD_UIO1 |

UIO1 Bit 8信号 |

17 |

UIO1_09 |

In/Out |

VDD_UIO1 |

UIO1 Bit 9信号 |

18 |

UIO1_10 |

In/Out |

VDD_UIO1 |

UIO1 Bit 10信号 |

19 |

UIO1_11 |

In/Out |

VDD_UIO1 |

UIO1 Bit 11信号 |

20 |

UIO1_12 |

In/Out |

VDD_UIO1 |

UIO1 Bit 12信号 |

21 |

UIO1_13 |

In/Out |

VDD_UIO1 |

UIO1 Bit 13信号 |

22 |

UIO1_14 |

In/Out |

VDD_UIO1 |

UIO1 Bit 14信号 |

23 |

UIO1_15 |

In/Out |

VDD_UIO1 |

UIO1 Bit 15信号 |

24 |

GND |

Power |

- |

電源 (GND) |

25 |

UIO3_00 / UIIO4_06 |

In/Out |

VDD_3V3_SYS / VDD_3V3_IO[2] |

UIO3 Bit 0信号。ハードウェアオプションで UIO4 Bit 6信号との接続変更が可能。 |

26 |

UIO3_01 / UIIO4_07 |

In/Out |

VDD_3V3_SYS / VDD_3V3_IO[2] |

UIO3 Bit 1信号。ハードウェアオプションで UIO4 Bit 7信号との接続変更が可能。 |

27 |

UIO3_02 / UIIO4_08 |

In/Out |

VDD_3V3_SYS / VDD_3V3_IO[2] |

UIO3 Bit 2信号。ハードウェアオプションで UIO4 Bit 8信号との接続変更が可能。 |

28 |

UIO4_00 |

Input |

VDD_3V3_IO |

UIO4 Bit 0信号 |

29 |

GND |

Power |

- |

電源 (GND) |

30 |

TRCH_UART_TX / UIO4_09 |

Input |

VDD_3V3_SYS / VDD_3V3_IO[2] |

TRCH UART TX信号。ハードウェアオプションで UIO4 Bit 9信号との接続変更が可能。 |

31 |

TRCH_UART_RX / UIO4_10 |

Output |

VDD_3V3_SYS / VDD_3V3_IO[2] |

TRCH UART RX信号。ハードウェアオプションで UIO4 Bit 10信号との接続変更が可能。 |

32 |

VDD_3V3_SYS |

Power |

- |

OBCからの3.3V電源 (VDD_3V3_SYS) |

33 |

GND |

Power |

- |

電源 (GND) |

34 |

I2C_EXT_SCL |

Input |

VDD_3V3_SYS |

External I2C SCL信号 |

35 |

I2C_EXT_SDA |

In/Out |

VDD_3V3_SYS |

External I2C SDA信号 |

36 |

WDOG_OUT / UIO4_11 |

Input |

VDD_3V3_SYS / VDD_3V3_IO[2] |

Watchdog入力信号。ハードウェアオプションで UIO4 Bit 11信号との接続変更が可能。 |

37 |

VDD_3V3_IO_P37 |

Power |

- |

OBCからの3.3V電源 (VDD_3V3_IO) |

38 |

VDD_3V3_IO_P38 |

Power |

- |

OBCからの3.3V電源 (VDD_3V3_IO) |

39 |

VDD_UIO1_P39 |

Power |

- |

UIO1用の電源 (VDD_UIO1) |

40 |

VDD_UIO1_P40 |

Power |

- |

UIO1用の電源 (VDD_UIO1) |

| ピン番号 | ピン名 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

41 |

VDD_UIO2_P41 |

Power |

- |

UIO2用の電源 (VDD_UIO2) |

42 |

VDD_UIO2_P42 |

Power |

- |

UIO2用の電源 (VDD_UIO2) |

43 |

UIO4_05 |

In/Out |

VDD_3V3_IO |

UIO4 Bit 5信号 |

44 |

UIO4_04 |

In/Out |

VDD_3V3_IO |

UIO4 Bit 4信号 |

45 |

UIO4_03 |

In/Out |

VDD_3V3_IO |

UIO4 Bit 3信号 |

46 |

UIO4_02 |

In/Out |

VDD_3V3_IO |

UIO4 Bit 2信号 |

47 |

UIO4_01 |

In/Out |

VDD_3V3_IO |

UIO4 Bit 1信号 |

48 |

GND |

Power |

- |

電源 (GND) |

49 |

ICSP_PGD |

In/Out |

VDD_3V3_SYS |

TRCH PGD信号 |

50 |

ICSP_PGC |

In/Out |

VDD_3V3_SYS |

TRCH PGC信号 |

51 |

ICSP_MCLR_B |

Output |

VDD_3V3_SYS |

TRCH MCLR_B信号 |

52 |

GND |

Power |

- |

電源 (GND) |

53 |

FPGA_TCK |

Output |

VDD_3V3_IO |

FPGA JTAG TCK信号 |

54 |

FPGA_TDO |

Input |

VDD_3V3_IO |

FPGA JTAG TDO信号 |

55 |

FPGA_TDI |

Output |

VDD_3V3_IO |

FPGA JTAG TDI信号 |

56 |

FPGA_TMS |

Output |

VDD_3V3_IO |

FPGA JTAG TMS信号 |

57 |

GND |

Power |

- |

電源 (GND) |

58 |

UIO2_15 |

In/Out |

VDD_UIO2 |

UIO2 Bit 15信号 |

59 |

UIO2_14 |

In/Out |

VDD_UIO2 |

UIO2 Bit 14信号 |

60 |

UIO2_13 |

In/Out |

VDD_UIO2 |

UIO2 Bit 13信号 |

61 |

UIO2_12 |

In/Out |

VDD_UIO2 |

UIO2 Bit 12信号 |

62 |

UIO2_11 |

In/Out |

VDD_UIO2 |

UIO2 Bit 11信号 |

63 |

UIO2_10 |

In/Out |

VDD_UIO2 |

UIO2 Bit 10信号 |

64 |

UIO2_09 |

In/Out |

VDD_UIO2 |

UIO2 Bit 9信号 |

65 |

UIO2_08 |

In/Out |

VDD_UIO2 |

UIO2 Bit 8信号 |

66 |

GND |

Power |

- |

電源 (GND) |

67 |

UIO2_07 |

In/Out |

VDD_UIO2 |

UIO2 Bit 7信号 |

68 |

UIO2_06 |

In/Out |

VDD_UIO2 |

UIO2 Bit 6信号 |

69 |

UIO2_05 |

In/Out |

VDD_UIO2 |

UIO2 Bit 5信号 |

70 |

UIO2_04 |

In/Out |

VDD_UIO2 |

UIO2 Bit 4信号 |

71 |

UIO2_03 |

In/Out |

VDD_UIO2 |

UIO2 Bit 3信号 |

72 |

UIO2_02 |

In/Out |

VDD_UIO2 |

UIO2 Bit 2信号 |

73 |

UIO2_01 |

In/Out |

VDD_UIO2 |

UIO2 Bit 1信号 |

74 |

UIO2_00 |

In/Out |

VDD_UIO2 |

UIO2 Bit 0信号 |

75 |

GND |

Power |

- |

電源 (GND) |

76 |

CANL |

In/Out |

- |

CAN L信号 |

77 |

CANH |

In/Out |

- |

CAN H信号 |

78 |

VIN_B_P78 |

Power |

- |

OBCの主電源(B系統) |

79 |

VIN_B_P79 |

Power |

- |

OBCの主電源(B系統) |

80 |

VIN_B_P80 |

Power |

- |

OBCの主電源(B系統) |

7.2. DEBUG インタフェース(CON2)

CON2はFPGAとTRCHのDEBUGインタフェースです。FTDI社製 FT4232H-56Qを経由し、FPGAとTRCHの各種 デバッグ機能を実現します。 FT4232HのChannelの割り当ては以下の通りです。

| Channel | Function |

|---|---|

A |

FPGA JTAG (AMD製 Platform cable USB IIと同等の機能) |

B |

CPU JTAG |

C |

FPGA UART |

D |

TRCH UART |

DEBUGインタフェースをVivadoがインストールされている PCに接続することでFPGAの書き込みを行うことができます。 そのためPlatform cable USB IIは別途準備していただく必要はありません。

これらの機能は、後述するユーザースイッチ (SW1)によって機能の有効/無効を切り替が必要ものがあります。詳細はユーザースイッチ (SW1)を参照してください。

搭載コネクタ:105017-0001(Molex)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

FTDI_VBUS |

Power |

- |

USB電源入力(FTDI_VBUS) |

2 |

FTDI_USB_DM |

In/Out |

- |

USBマイナス側信号 |

3 |

FTDI_USB_DP |

In/Out |

- |

USBプラス側信号 |

4 |

FTDI_ID |

Input |

- |

未接続 |

5 |

GND |

Power |

- |

電源(GND) |

7.3. FPGA JTAG インタフェース(CON3)

CON3はJTAGインタフェースであり、OBCのJTAGポートへ接続されています。

以下を接続する場合に使用することができます。

-

AMD(旧 Xilinx)社製 Platform cable USB II Flying Wire Adapter

-

Digilent社製 JTAG-HS2 Programming Cable

|

DEBUGインタフェース(CON2)を用いないでFPGA JTAGにアクセスする場合に使用します。CON3を使用する場合は、DEBUGインタフェースにUSBケーブルを接続しないでください。 |

搭載可能コネクタ:TSW-106-07-L-S(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

FPGA_TMS |

Input |

VDD_3V3_IO |

JTAG モード選択 |

2 |

FPGA_TDI |

Input |

VDD_3V3_IO |

JTAG データ入力 |

3 |

FPGA_TDO |

Output |

VDD_3V3_IO |

JTAG データ出力 |

4 |

FPGA_TCK |

Input |

VDD_3V3_IO |

JTAG クロック |

5 |

GND |

Power |

- |

電源(GND) |

6 |

VDD_3V3_IO |

Power |

- |

電源(VDD_3V3_IO) |

7.4. TRCH ICSP インタフェース(CON4)

CON4はTRCHのICSPインタフェースであり、OBCのICSPポートへ接続されています。

ピン配列はMicrochip社製 MPLAB PICkit 4または5に対応しており、付属の両端ロングピンヘッダを使用することで、本体を直接接続することが可能です。

搭載コネクタ:SSQ-108-02-G-S-RA(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

ICSP_MCLR_B |

Input |

VDD_3V3_SYS |

ICSP VPP/MCLR |

2 |

VDD_3V3_SYS |

Power |

- |

電源(VDD_3V3_SYS) |

3 |

GND |

Power |

- |

電源(GND) |

4 |

ICSP_PGD |

Input |

VDD_3V3_SYS |

ICSP データ入力 |

5 |

ICSP_PGC |

Input |

VDD_3V3_SYS |

ICSP クロック |

6 |

NC |

- |

- |

未接続 |

7 |

NC |

- |

- |

未接続 |

8 |

NC |

- |

- |

未接続 |

7.5. CAN インタフェース(CON5)

CON5はCAN通信のインタフェースであり、OBCのCANポートへ接続されています。

OBC上のTRCHおよびFPGAとの通信が可能です。

搭載コネクタ:TB002-500-03BE(Same Sky)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

CANL |

In/Out |

- |

CAN L信号 |

2 |

CANH |

In/Out |

- |

CAN H信号 |

3 |

GND |

Power |

- |

電源(GND) |

7.6. UIO1 インタフェース(CON6)

CON6はUIO1のインタフェースであり、OBCのUIO1ポートへ接続されています。

OBC上のFPGAへ接続されており、ユーザーが自由に使用できる信号です。

搭載可能コネクタ:SSQ-116-01-G-S(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

UIO1_00 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

2 |

UIO1_01 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

3 |

UIO1_02 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

4 |

UIO1_03 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

5 |

UIO1_04 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

6 |

UIO1_05 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

7 |

UIO1_06 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

8 |

UIO1_07 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

9 |

UIO1_08 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

10 |

UIO1_09 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

11 |

UIO1_10 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

12 |

UIO1_11 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

13 |

UIO1_12 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

14 |

UIO1_13 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

15 |

UIO1_14 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

16 |

UIO1_15 |

In/Out |

VDD_UIO1 |

UIO1 入出力 |

7.7. UIO1 Power & GND インタフェース(CON7)

CON7はUIO1用の電源およびGNDのインタフェースです。

搭載可能コネクタ:SSQ-103-01-G-S x2 または SSQ-106-01-G-S(Samtec)

| ピン番号 | ピン名称 |

|---|---|

1 |

GND |

2 |

GND |

3 |

GND |

4 |

VDD_UIO1 |

5 |

VDD_UIO1 |

6 |

VDD_UIO1 |

7.8. UIO2 インタフェース(CON8)

CON8はUIO2のインタフェースであり、OBCのUIO2ポートへ接続されています。

OBC上のFPGAへ接続されており、ユーザーが自由に使用できる信号です。

搭載可能コネクタ:SSQ-116-01-G-S(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

UIO2_00 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

2 |

UIO2_01 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

3 |

UIO2_02 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

4 |

UIO2_03 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

5 |

UIO2_04 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

6 |

UIO2_05 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

7 |

UIO2_06 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

8 |

UIO2_07 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

9 |

UIO2_08 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

10 |

UIO2_09 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

11 |

UIO2_10 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

12 |

UIO2_11 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

13 |

UIO2_12 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

14 |

UIO2_13 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

15 |

UIO2_14 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

16 |

UIO2_15 |

In/Out |

VDD_UIO2 |

UIO2 入出力 |

7.9. UIO2 Power & GND インタフェース(CON9)

CON9はUIO2用の電源およびGNDのインタフェースです。

搭載可能コネクタ:SSQ-103-01-G-S x2 または SSQ-106-01-G-S(Samtec)

| ピン番号 | ピン名称 |

|---|---|

1 |

GND |

2 |

GND |

3 |

GND |

4 |

VDD_UIO2 |

5 |

VDD_UIO2 |

6 |

VDD_UIO2 |

7.10. UIO3 インタフェース(CON10)

CON10はUIO3, TRCH UART, Watchdog出力信号, External I2Cのインタフェースであり、OBCへ接続されています。

OBCのハードウェアオプションによりUIO4に変わる信号があるため、使用する際は電源ドメインの違いにご注意ください。

搭載可能コネクタ:SSQ-116-01-G-S(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

UIO3_00 |

In/Out |

VDD_3V3_SYS |

UIO3 入出力 |

UIO4_06 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

2 |

UIO3_01 |

In/Out |

VDD_3V3_SYS |

UIO3 入出力 |

UIO4_07 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

3 |

UIO3_02 |

In/Out |

VDD_3V3_SYS |

UIO3 入出力 |

UIO4_08 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

4 |

TRCH_UART_TX |

Output |

VDD_3V3_SYS |

TRCH UART TX信号 |

UIO4_09 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

5 |

TRCH_UART_RX |

Input |

VDD_3V3_SYS |

TRCH UART RX信号 |

UIO4_10 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

6 |

WDOG_OUT |

In/Out |

VDD_3V3_SYS |

Watchdog出力信号 |

UIO4_11 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

|

7 |

I2C_EXT_SCL |

Output |

VDD_3V3_SYS |

External I2C クロック |

8 |

I2C_EXT_SDA |

In/Out |

VDD_3V3_SYS |

External I2C データ信号 |

7.11. UIO3 Power & GND インタフェース(CON11)

CON11はUIO3, TRCH UART, Watchdog出力信号, External I2C用の電源およびGNDのインタフェースです。

OBCのハードウェアオプションによりUIO4_XXに選択されている信号については、必ずUIO4 Power & GND インタフェース(CON13)の電源をご利用ください。

搭載可能コネクタ:SSQ-103-01-G-S x2 または SSQ-106-01-G-S(Samtec)

| ピン番号 | ピン名称 |

|---|---|

1 |

GND |

2 |

GND |

3 |

GND |

4 |

VDD_3V3_SYS |

5 |

VDD_3V3_SYS |

6 |

VDD_3V3_SYS |

7.12. UIO4 インタフェース(CON12)

CON12はUIO4のインタフェースであり、OBCのUIO4ポートへ接続されています。

OBC上のFPGAへ接続されており、ユーザーが自由に使用できる信号です。

搭載可能コネクタ:SSQ-116-01-G-S(Samtec)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

UIO4_00 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

2 |

UIO4_01 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

3 |

UIO4_02 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

4 |

UIO4_03 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

5 |

UIO4_04 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

6 |

UIO4_05 |

In/Out |

VDD_3V3_IO |

UIO4 入出力 |

7.13. UIO4 Power & GND インタフェース(CON13)

CON13はUIO4用の電源およびGNDのインタフェースです。

搭載可能コネクタ:SSQ-103-01-G-S x2 または SSQ-106-01-G-S(Samtec)

| ピン番号 | ピン名称 |

|---|---|

1 |

GND |

2 |

GND |

3 |

GND |

4 |

VDD_3V3_IO |

5 |

VDD_3V3_IO |

6 |

VDD_3V3_IO |

7.14. SC Busホスト インタフェース(CON15)

SC Busを使用する場合、OBCはホストとしてもデバイスとしても利用が可能です。

|

SC BusはSpace Cubicsにて開発中の機能です。FPGAにULPI規格に準拠したUSBコアを実装する事でUSBとして、このインタフェースはUSBとして使用する事ができます。 |

CON15はSC Busのホストインタフェースです。

Data (D+/D-)ラインはOBCと接続されており、CON16と共用しています。

VBUSはCON17からの電圧がそのまま出力されますが、出力電流に比例して電圧降下します。またCON16へUSBプラグが挿入されると、VBUS経路上のパワースイッチが制御され、VBUSの出力が切断されます。

CON15とCON16を併用することは想定していないため、CON15を使用する場合、CON16へUSBプラグを挿入しないでください。

搭載コネクタ:67643-2911(Molex)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

VBUS_A |

Power |

- |

USB電源出力(VBUS_A) |

2 |

ULPI_DM |

In/Out |

- |

USBマイナス側信号 |

3 |

ULPI_DP |

In/Out |

- |

USBプラス側信号 |

4 |

GND |

Power |

- |

電源(GND) |

7.15. SC Busデバイス インタフェース(CON16)

SC Busを使用する場合、OBCはホストとしてもデバイスとしても利用が可能です。

|

SC BusはSpace Cubicsにて開発中の機能です。FPGAにULPI規格に準拠したUSBコアを実装する事でUSBとして、このインタフェースはUSBとして使用する事ができます。 |

CON16はSC Busのデバイスインタフェースです。

Data (D+/D-)ラインはOBCと接続されており、CON15と共用しています。

VBUSはCON15のVBUS経路上にあるパワースイッチのEN端子を制御するFET (Q4)のゲートへ接続されているため、VBUSが印加されるとCON15のVBUS出力が切断されます。

CON15とCON16を併用することは想定していないため、CON16を使用する場合、CON15へUSBプラグを挿入しないでください。

搭載コネクタ:105017-0001(Molex)

| ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|

1 |

VBUS_B |

Power |

- |

USB電源入力(VBUS_B) |

2 |

ULPI_DM |

In/Out |

- |

USBマイナス側信号 |

3 |

ULPI_DP |

In/Out |

- |

USBプラス側信号 |

4 |

ULPI_ID |

Input |

- |

未接続 |

5 |

GND |

Power |

- |

電源(GND) |

7.16. 電源入力 インタフェース(CON17)

CON17は+5V電源の入力インタフェースで、DCジャックを採用しています。

対応するACアダプターのプラグ仕様は、外径5.5mm、内径2.1mmのセンタープラスです。

OBCを含め、全ての主電源となります。

搭載コネクタ:PJ-002AH(Same Sky)

7.17. 電源入力 インタフェース (VIN_A)(CON18)

CON18は+5V電源の入力インタフェースで、5mmピッチ2ピンの端子台を採用しています。

以下の場合に使用します。

-

ユーザーが用意する電源機器でOBCを動作させたい場合

-

OBCをVIN_Aのみで動作させたい場合

-

VDD_3V3_DCDCを使用したい場合

また、R110へ3216サイズの0Ω抵抗を実装することで、電源入力の保護回路 (IC11)を介さず、直接 OBCへ電圧を印加することが可能です。

搭載コネクタ:TB003-500-P02BE(Same Sky)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

GND |

電源(GND) |

2 |

VIN_A_TRM |

電源(VIN_Aへの入力) |

7.18. 電源入力 インタフェース (VIN_B)(CON19)

CON19は+5V電源の入力インタフェースで、5mmピッチ2ピンの端子台を採用しています。

以下の場合に使用します。

-

ユーザーが用意する電源機器でOBCを動作させたい場合

-

OBCをVIN_Bのみで動作させたい場合

また、R122へ3216サイズの0Ω抵抗を実装することで、電源入力の保護回路 (IC12)を介さず、直接 OBCへ電圧を印加することが可能です。

搭載コネクタ:TB003-500-P02BE(Same Sky)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

GND |

電源(GND) |

2 |

VIN_B_TRM |

電源(VIN_Bへの入力) |

7.19. 電源入力 インタフェース (VDD_UIO1)(CON20)

CON20は VDD_UIO1 への入力インタフェースで、5mmピッチ2ピンの端子台を採用しています。

VDD_UIO1として VDD_3V3_IO や VDD_3V3_DCDC を使用せず、ユーザーが任意の電圧へ設定したい場合に使用します。

搭載コネクタ:TB003-500-P02BE(Same Sky)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

GND |

電源(GND) |

2 |

VDD_UIO1_TRM |

電源(VDD_UIO1への入力) |

7.20. 電源入力 インタフェース (VDD_UIO2)(CON21)

CON21は VDD_UIO2 への入力インタフェースで、5mmピッチ2ピンの端子台を採用しています。

VDD_UIO2 として VDD_3V3_IO や VDD_3V3_DCDC を使用せず、ユーザーが任意の電圧へ設定したい場合に使用します。

搭載コネクタ:TB003-500-P02BE(Same Sky)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

GND |

電源(GND) |

2 |

VDD_UIO2_TRM |

電源(VDD_UIO2への入力) |

7.21. 降圧DC/DCコンバータ出力 インタフェース(CON22)

CON22は VDD_3V3_DCDC の出力インタフェースです。VDD_UIO1 および VDD_UIO2 の電源以外の用途での使用を想定しています。最大出力電流は 2A です。

搭載可能コネクタ:10129378-902001BLF(Amphenol CS)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

GND |

電源(GND) |

2 |

VDD_3V3_DCDC |

電源(VDD_3V3_DCDC出力) |

7.22. CAN終端抵抗切替 インタフェース(JP1)

JP1はCAN通信経路上のOBC側の終端抵抗 (120Ω)の有無を切り替えることができるインタフェースです。

OBCには終端抵抗が実装されていないことから、Dev Boardの初期仕様ではJP1にジャンパーソケットが挿入され、OBC側が終端されています。

Dev Board外で別途終端する場合はジャンパーソケットを外してください。

搭載コネクタ:10129378-902001BLF(Amphenol CS)

7.23. 電源入力切替 インタフェース (VIN_A)(JP2)

JP2はVIN_Aへの入力をCON17またはCON18へ切り替えるためのインタフェースです。

搭載コネクタ:10129378-903001BLF(Amphenol CS)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

5V |

電源(CON17からの入力) |

2 |

VIN_A_CM |

電源(VIN_Aへ繋がる共通の端子) |

3 |

VIN_A_TRM |

電源(CON18からの入力) |

| モード | ピン接続 | 説明 |

|---|---|---|

Mode1(初期) |

1-2 |

VIN_Aへの入力をCON17から供給 |

Mode2 |

2-3 |

VIN_Aへの入力をCON18から供給 |

7.24. 電源入力切替 インタフェース (VIN_B)(JP3)

JP3はVIN_Bへの入力をCON17またはCON19へ切り替えるためのインタフェースです。

搭載コネクタ:10129378-903001BLF(Amphenol CS)

| ピン番号 | ピン名称 | 説明 |

|---|---|---|

1 |

5V |

電源(CON17からの入力) |

2 |

VIN_B_CM |

電源(VIN_Bへ繋がる共通の端子) |

3 |

VIN_B_TRM |

電源(CON19からの入力) |

| モード | ピン接続 | 説明 |

|---|---|---|

Mode1(初期) |

1-2 |

VIN_Bへの入力をCON17から供給 |

Mode2 |

2-3 |

VIN_Bへの入力をCON19から供給 |

7.25. 電源入力切替 インタフェース (VDD_UIO1)(JP4)

JP4は VDD_UIO1 への電源を VDD_3V3_IO, VDD_3V3_DCDC, CON20の中から選択することができるインタフェースです。

Dev Boardの初期仕様では、ジャンパーソケットによりVDD_3V3_IOが選択されています。

搭載コネクタ:10129381-906001BLF(Amphenol CS)

| ピン番号 | ピン名称 | 説明 | ピン番号 | ピン名称 | 説明 |

|---|---|---|---|---|---|

1 |

VDD_3V3_IO |

電源(VDD_3V3_IO入力) |

2 |

VDD_UIO1_IN |

電源(VDD_UIO1へ繋がる共通の端子) |

3 |

VDD_UIO1_IN |

電源(VDD_UIO1へ繋がる共通の端子) |

4 |

VDD_3V3_DCDC |

電源(VDD_3V3_DCDC入力) |

5 |

VDD_UIO1_TRM |

電源(CON20からの入力) |

6 |

VDD_UIO1_IN |

電源(VDD_UIO1へ繋がる共通の端子) |

| モード | ピン接続 | 説明 |

|---|---|---|

Mode1(初期) |

1-2 |

VDD_UIO1への電源をVDD_3V3_IOから供給 |

Mode2 |

3-4 |

VDD_UIO1への電源をVDD_3V3_DCDCから供給 |

Mode3 |

5-6 |

VDD_UIO1への電源をCON20から供給 |

7.26. 電源入力切替 インタフェース (VDD_UIO2)(JP5)

JP5は VDD_UIO2 への電源を VDD_3V3_IO, VDD_3V3_DCDC, CON21の中から選択することができるインタフェースです。

Dev Boardの初期仕様では、ジャンパーソケットによりVDD_3V3_IOが選択されています。

搭載コネクタ:10129381-906001BLF(Amphenol CS)

| ピン番号 | ピン名称 | 説明 | ピン番号 | ピン名称 | 説明 |

|---|---|---|---|---|---|

1 |

VDD_3V3_IO |

電源(VDD_3V3_IO入力) |

2 |

VDD_UIO2_IN |

電源(VDD_UIO2へ繋がる共通の端子) |

3 |

VDD_UIO2_IN |

電源(VDD_UIO2へ繋がる共通の端子) |

4 |

VDD_3V3_DCDC |

電源(VDD_3V3_DCDC入力) |

5 |

VDD_UIO2_TRM |

電源(CON21からの入力) |

6 |

VDD_UIO2_IN |

電源(VDD_UIO2へ繋がる共通の端子) |

| モード | ピン接続 | 説明 |

|---|---|---|

Mode1(初期) |

1-2 |

VDD_UIO2への電源をVDD_3V3_IOから供給 |

Mode2 |

3-4 |

VDD_UIO2への電源をVDD_3V3_DCDCから供給 |

Mode3 |

5-6 |

VDD_UIO2への電源をCON21から供給 |

7.27. ユーザースイッチ(SW1)

SW1はOBCと以下の回路の間の接続を制御するためのスイッチです。

-

High-Speed USB Bridge FT4232H-56Q (IC2)

-

ユーザーが自由に使用できる温度センサ回路(ユーザー温度センサ)

-

ユーザーが自由に使用できるLED回路(ユーザー LED)

初期設定はBit 3,4のみがONで、その他のBitはOFFです。使用する回路のBitを手動で切り替えてください。

手動で切り替える場合、指では操作しづらいため、ピンセットなどの先の尖った道具を使用してください。

また、OBCからSW1へ繋がる信号線はUniversal Areaへも分岐しています。上記の回路に接続される信号線をUniversal Areaで使用する際はご留意ください。

搭載部品:219-10MSTR(CTS Electrocomponents)

| Bit番号 | ピン番号 | ピン名称 | I/O | 電源ドメイン | 説明 |

|---|---|---|---|---|---|

1 |

1,20 |

TRCH_UART_RX / UIO4_10 |

Input |

VDD_3V3_SYS / VDD_3V3_IO |

USBインタフェース(CON2)によるTRCH UARTへの通信 (ON:可 / OFF:不可) |

2 |

2,19 |

TRCH_UART_TX / UIO4_09 |

Input |

VDD_3V3_SYS / VDD_3V3_IO |

|

3 |

3,18 |

UIO4_04 |

In/Out |

VDD_3V3_IO |

USBインタフェース(CON2)によるFPGA UARTへの通信 (ON:可 / OFF:不可) (※UIO4_03,04へFPGA UARTを割り当てている場合) |

4 |

4,17 |

UIO4_03 |

In/Out |

VDD_3V3_IO |

|

5 |

5,16 |

UIO4_02 |

In/Out |

VDD_3V3_IO |

USBインタフェース(CON2)によるCPU JTAGへの通信 (ON:可 / OFF:不可) (※UIO4_01,02へCPU JTAGを割り当てている場合) |

6 |

6,15 |

UIO4_01 |

In/Out |

VDD_3V3_IO |

|

7 |

7,14 |

I2C_EXT_SCL |

Output |

VDD_3V3_SYS |

External I2Cによるユーザー温度センサからの温度データ取得 (ON:可 / OFF:不可) |

8 |

8,13 |

I2C_EXT_SDA |

In/Out |

VDD_3V3_SYS |

|

9 |

9,12 |

UIO2_14 |

In/Out |

VDD_UIO2 |

UIO2_14に対するプルダウン(1kΩ) (ON:有 / OFF:無) |

10 |

10,11 |

UIO2_15 |

In/Out |

VDD_UIO2 |

UIO2_15によるユーザーLED(LED11)の制御 (ON:可 / OFF:不可) |

7.28. 主電源入力 ON/OFF(SW2)

SW2は入力保護回路 (IC11, IC12)のEN端子を制御し、CON17~19とVIN_AおよびVIN_Bとの間を接続または切断できるインタフェースです。

Dev Board上のシルク表示の『ON』側へSW2のトグルを動かすと接続され、『OFF』側へ動かすと切断されます。

初期設定は『OFF』です。

搭載部品:SSSF011700(Alps Alpine)

| 番号 | 名称 |

|---|---|

1 |

主電源をOFFします。 |

2 |

主電源をONします。 |

7.29. 電源 LED(LED1~8)

LED1~8は各電源のステータスを示すLEDです。点灯は正常なステータスを示します。

搭載部品:SML-D12M8WT86(ROHM)

| 部品番号 | LED色 | 対応する電源 |

|---|---|---|

LED1 |

黄緑色 |

VIN_A |

LED2 |

黄緑色 |

VIN_B |

LED3 |

黄緑色 |

VDD_3V3_SYS |

LED4 |

黄緑色 |

VDD_3V3_IO |

LED5 |

黄緑色 |

VDD_3V3_DCDC |

LED6 |

黄緑色 |

VDD_UIO1 |

LED7 |

黄緑色 |

VDD_UIO2 |

LED8 |

黄緑色 |

VBUS_A |

7.30. ユーザー LED(LED11)

LED11はユーザーが自由に使用できるLEDです。

搭載部品:SML-D12M8WT86(ROHM)

| 部品番号 | LED色 | 説明 |

|---|---|---|

LED11 |

黄緑色 |

SW1を経由してOBCのUIO2_15へ接続 |

7.31. VDD_UIOについて

VDD_UIO1およびVDD_UIO2には任意の電圧を印加して使用することができます。

ただしFPGAのIO電源はFPGAの電源投入シーケンスに従う必要があり、VDD_3V3_IOがHighになった後に電圧を印加することで電源シーケンスを守ることができます。

Dev BoardではVDD_UIOライン上にパワースイッチ(IC14, IC15)を設けることで、電源シーケンスを守らずにFPGAのIO電圧を印加する事態を防止できます。

またVDD_3V3_IOには電圧値や電流容量の制約があることから、JP4, JP5により、VDD_UIOへの入力を以下の3パターンへ切り替えることを可能にしています。

VDD_UIO = VDD_3V3_IO

VDD_UIO = VDD_3V3_DCDC

VDD_UIO = Block Terminal Input