Overview

What is SC-OBC Module V1

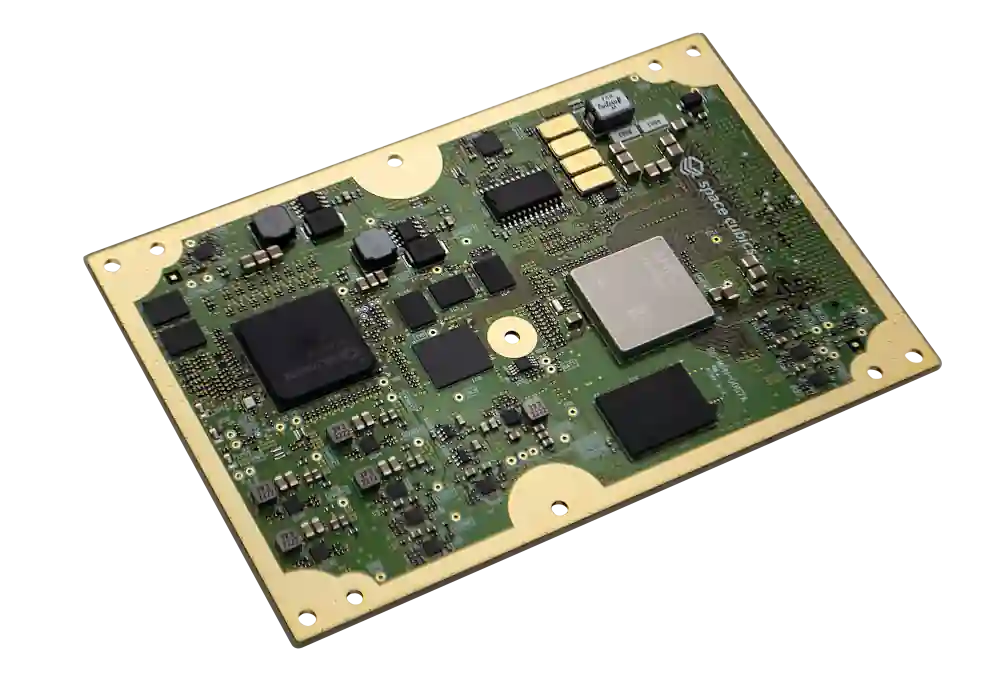

The SC-OBC Module V1 is a modular onboard computer for space missions that need reliable real-time control and edge processing. It is built around an AMD Versal Adaptive SoC and a Microchip IGLOO2 FPGA, and is designed for harsh environments such as Earth orbit and lunar missions.

On the Versal side, the SC-OBC V1 leverages the device’s heterogeneous architecture, combining dual-core Arm Cortex-A72 application processors and dual-core Arm Cortex-R5F real-time processors with programmable logic, AI Engines, and DSP engines. This enables on-orbit workloads such as object detection, image compression and segmentation, and high-speed signal processing, while keeping flight-critical tasks on the real-time processors with a predictable scheduling model.

On the IGLOO2 side, the SC-OBC V1 uses the device as the board’s safety processor, supervising the main system, providing independent watchdog and fault-management paths, and coordinating safe-mode transitions to improve fault tolerance.

Evaluation Board

Because SC-OBC Module V1 is a modular OBC, users must at least have some kind of carrier board to power the OBC. In this document we assume that you have V1 Carrier Board SC-MPN-0062A.

About This Document

This document describes the software for the SC-OBC Module V1 and how it is organized across the device’s heterogeneous compute resources. Because the module includes multiple processor classes, each has its own section and build, boot, and validation guidance.

The first section covers setup and preparation. In addition to the SC-OBC Module V1, you will need a few items to use the OBC. You will also set up your development environment.

The section on the AMD Versal application processors (dual Arm Cortex-A72) explains how to build U-Boot and Linux with the Yocto Project or AMD PetaLinux, and how to boot from an SD card. It outlines the standard Versal boot flow where PLM hands off to TF-A, then U-Boot loads Linux, and it notes that SD boot is a supported sequence.

The section on the AMD Versal real-time processors (dual Arm Cortex-R5F) focuses on Zephyr RTOS for flight-critical workloads that require deterministic behavior and predictable scheduling. It covers building and running Zephyr on the R5F cores in lockstep mode.